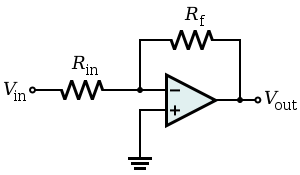

음의 피드백을 사용하는 연산 증폭기 회로를 만들 때 다음과 같이하십시오.

... 우리가 가정하여, 매우 용이하게 회로를 분석 할 수 네거티브 피드백 때문에 (또한, 연산 증폭기를 가정 할 때, 물론, 이상적이다).

이러한 단순화 된 모델이 고장 나는 명백한 고정밀 사례 외에 언제, 언제 이것이 유효하지 않습니까?

예를 들어, 피드백 저항을 커패시터, 인덕터, 다이오드 (일반 실리콘 다이오드, 제너 다이오드 등) 또는 이들과 다른 공통 회로 요소의 조합과 같은 다른 요소로 대체하는 경우,이 위치를 어떻게 알 수 있습니까? 단순화가 유효합니까?

또한 피드백 요소로 저항을 유지하더라도 저항이 매우 높아지면 언젠가는 개방 회로로 간주 할 수 있으므로이 모델은 분명히 어딘가에서 고장납니다.

따라서 문제는 다음과 같습니다.이 근사값은 유용한 결과를 제공하기 위해 "충분히 참"이란 제약 조건은 무엇입니까?

편집하다:

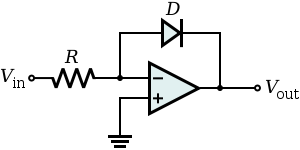

다른 예를 들어, 기본 반전 로그 증폭기 회로를 고려하십시오.

Shockley 다이오드 방정식을 풀면

vD의 경우 (주로 관계가 1을 무시하면, 지수)는 다소 큰 것 같이

그런 다음 가상 단축 법을 사용하여 우리는 출력을위한 올바른 표현을 얻을 :

+및-단자가 회로에서의 연산 증폭기 사용과 독립적으로 동일합니다.