칩의 트랜지스터 수를 늘리면 속도가 어떻게 증가합니까?

답변:

이런 종류의 것들에 대해 궁금하다면 Noam Nisan 의 The Elements of Computing 과 Shimon Schocken (적어도 상반기)을 강력히 추천합니다 . 이 과정을 거친 후에는 관련된 부분을 충분히 이해하여 자신의 질문에 매우 자세히 답변 할 수 있습니다.

동반자 웹 사이트는 실제로 일부 샘플 장과 메모를 가지고있다. 매우 접근하기 쉬운 책입니다. 나는 아무 문제없이 스스로 공부를 한 다음, 대학에서 기본 텍스트로 사용한 새로운 수업을 들었습니다.

켄은 이미 그의 대답 에 몇 가지 이유를 요약 했습니다 . 더 확장하려면

- RAM보다 빠른 더 많은 캐시

분명히 더 큰 캐시 에는 더 많은 트랜지스터 가 필요합니다. 그러나 더 많은 트랜지스터를 사용하면 더 빠른 캐시 를 사용할 수도 있습니다 . CPU 캐시는이다 SRAM 통상적 6 트랜지스터 (6T SRAM AKA)로 만들어진다. 그러나 충분한 트랜지스터가있는 경우 6 개 이상의 트랜지스터 (예 : 8T, 10T SRAM)로 만든 더 빠르지 만 더 큰 SRAM 셀을 사용하는 것이 좋습니다.

- 단일 데이터 명령어보다 더 빠르게 처리하는 더 많은 SIMD 명령어

SIMD뿐만 아니라 모든 유형의 가속 명령. 예를 들어 최신 아키텍처에는 더 빠른 암호화 / 암호 해독을위한 AES 단위, 더 나은 수학 계산을위한 FMA (특히 디지털 신호 처리) 또는 더 빠른 가상 머신을위한 가상화가 있습니다. 더 많은 명령어를 지원한다는 것은 해독하고 실행하기 위해 더 많은 리소스가 필요하다는 것을 의미합니다

이것들은 분명하다

과거에는 FPU를위한 충분한 다이 면적이 없었기 때문에 사람들은 부동 소수점 산술에 대한 요구 사항이 높은 경우 별도의 다이를 구입해야합니다. 훨씬 더 많은 트랜지스터를 사용하면 FPU가 내장되어 부동 소수점 연산 속도를 크게 높일 수 있습니다

또한 최신 CPU는 슈퍼 스칼라 이며 명령 스트림이 선형이고 직렬 임에도 불구하고 독립적 인 데이터 조각 을 찾아서 미리 계산하여 여러 작업을 한 번 에 수행하려고합니다 . 병렬로 할 수있는 일이 많을수록 더 빨라집니다. 이를 위해 CPU에는 여러 개의 ALU가있을 수 있고 ALU에는 여러 개의 실행 단위가있을 수 있습니다. 예를 들어 CPU에 이전 세대의 4에 비해 5 개의 가산기가있는 경우 클럭 변경없이 가장 낙관적 인 상황에서 이미 25 % 더 빠르게 실행됩니다. 보다 정교한 CPU 는 비 순차적 실행 (대부분의 최신 고성능 CPU의 경우)

- 보다 정교한 분기 예측 로직 과 같은 더 나은 처리 로직

작업은 일반적으로 다양한 방법으로 수행 할 수 있습니다. 더 많은 트랜지스터가 있으면 더 빠른 기술을 사용할 수있는 더 많은 리소스가 있습니다. 몇 가지 간단한 예 :

비트 시프 팅 :

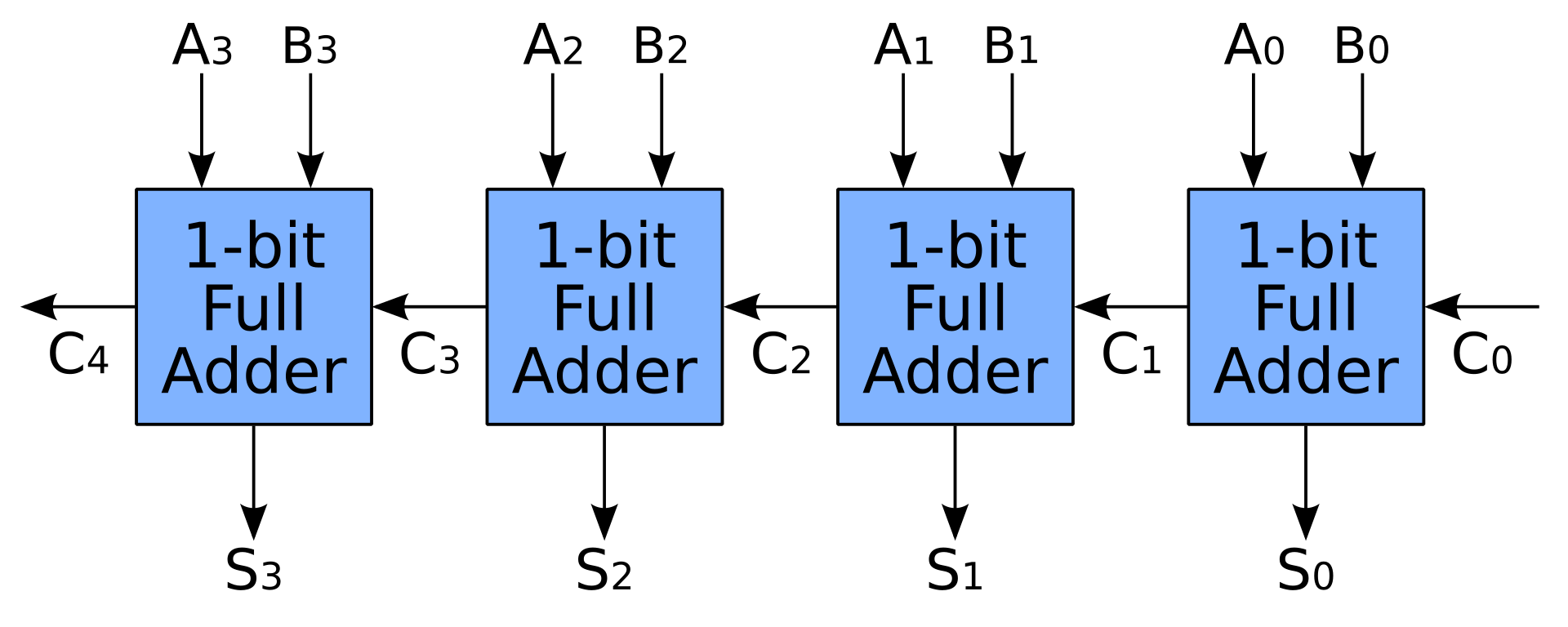

부가:

멀티 플라이어, 디바이더, 스케줄러와 같은 다른 장치에도 같은 내용이 적용됩니다. 예를 들어 조합 논리를 사용하여 단일 클록에서 매우 빠르게 곱셈을 수행 할 수 있습니다 . 질문 3 비트 승수 질문에서 간단한 예제를 볼 수 있습니다 -어떻게 작동합니까? . 그러나 필요한 트랜지스터는 입력 폭의 제곱으로 증가하므로 승수를 가진 작은 CPU는 승수 를 위해 많은 공간을 절약하기 위해 순차적 논리를 사용합니다.

오래된 멀티 플라이어 아키텍처는 쉬프터와 어큐뮬레이터를 사용하여 각 부분 제품,주기 당 하나의 부분 제품을 합산하여 다이 영역의 속도를 줄였습니다. 최신 멀티 플라이어 아키텍처는 (수정 된) Baugh-Wooley 알고리즘, Wallace 트리 또는 Dadda 멀티 플라이어를 사용하여 단일 제품으로 부분 제품을 함께 추가합니다. Wallace 트리 구현의 성능은 때때로 두 곱셈 중 하나를 수정 한 부스 인코딩으로 개선되어 합산해야하는 부분 곱의 수를 줄입니다.

https://en.wikipedia.org/wiki/Binary_multiplier#Implementations

거대한 트랜지스터 풀이 있으면 조합 논리를 사용하여 승수보다 훨씬 리소스를 많이 사용하는 FMA를 수행 할 수도 있습니다.

최신 컴퓨터에는 조합 논리로 구현 된 승수와 결과를 저장하는 가산기 및 누산기 레지스터로 구성된 전용 MAC이 포함될 수 있습니다. 레지스터의 출력은 가산기의 하나의 입력으로 피드백되어 각 클록 사이클에서 승수의 출력이 레지스터에 추가됩니다. 조합 승수에는 많은 양의 논리가 필요하지만 일반적인 이전 컴퓨터의 이동 및 추가 방법보다 훨씬 빠르게 제품을 계산할 수 있습니다.